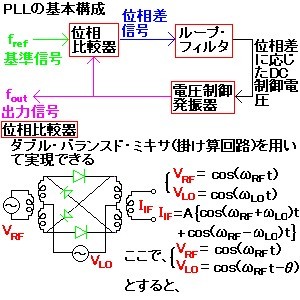

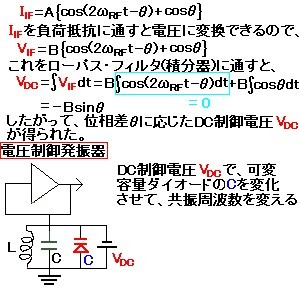

PLLとは、外部からの入力信号(基準信号)と同期した(位相差が等しい)出力信号を生成するための回路で、基本的な回路構成を図1に示す。PLLは、2つの信号間の位相を比較して位相差信号を生成する位相比較器、位相差信号をDC制御電圧に変換するループ・フィルタ(ローパス・フィルタ、積分器)、電圧制御発振器(VCO)で構成される。VCOの出力信号の位相が基準信号より遅れていれば(基準信号が図1のcos(ωRFt)、VCOの出力信号が図1のcos(ωRFt-θ)とすると)、位相比較器が位相差信号を生成する。それをループ・フィルタに通すことにより、位相差(図1のθ)の大きさに応じて、VCOの位相を進ませるDC制御電圧(図2の-Bsinθ)が生成され、VCOの出力信号の位相が進む。この動作が、連続的に実行されることにより、VCOの出力信号の位相と基準信号の位相との差がゼロになる(同期される)。PLL自身は、周波数を同期させているのではなく、位相を同期させているが、結果的に周波数も同期させることになる。

phase lock loop(位相ロック・ループ)

計測器の翻訳で、”phase lock loop”という言葉がよく出てくる。これは、「位相ロック・ループ」または「フェーズ・ロック・ループ」と訳される。PLLと略記されることもある。例えば、高周波デザイナーの為のVCO/PLL周波数シンセサイザ設計/評価手法がある。以下にPLLの動作原理を説明する。